Verilog HDL 어휘 규칙

대소문자 구별

주석 : //, /**/

식별자는 맨 앞에 영문자, 밑줄 ( _ )만 가능

모듈(Module): Verilog에서 디지털 회로는 모듈이라 불리는 논리 블록으로 구성됩니다. 각 모듈은 특정한 동작이나 블록을 나타냅니다.

선언(Declaration): 모듈 내에서 사용할 신호들을 선언합니다. 입력, 출력, 내부 레지스터 등을 정의할 수 있습니다.

할당(Assignment): 값을 할당하기 위해 assign 키워드나 = 기호를 사용합니다.

조합논리게이트(Combinational Logic Gates): AND, OR, NOT, NAND, NOR, XOR, XNOR 게이트 등이 Verilog에서 사용됩니다.

회로들의 동작적 모델링(Behavioral Modeling): always 블록을 사용하여 시간적인 동작을 정의합니다.

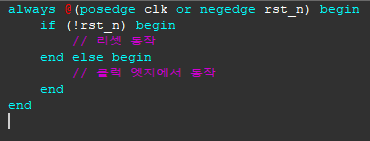

플립플롭(Flip-Flops): 디지털 회로에서 상태를 기억하기 위해 사용되는 플립플롭을 모델링할 수 있습니다.

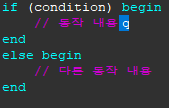

조건문(Conditional Statements): if, else, case 등을 사용하여 조건에 따른 동작을 정의합니다.

병렬 할당(Parallel Assignment): assign 키워드를 사용하여 병렬 할당을 정의합니다.

병렬 할당(Continuous Assignment): assign 키워드를 사용하여 회로에 대한 병렬 할당을 정의합니다. 이는 조합 논리 회로를 나타냅니다.

모듈 인스턴스화(Module Instantiation): 모듈을 다른 모듈 안에서 사용할 때 사용됩니다. 모듈 인스턴스화는 다음과 같이 이루어집니다.

파라미터(Parameter): 모듈이나 회로의 일부 특성을 매개변수화하려면 parameter를 사용합니다.

반복문(Loop): for 루프를 사용하여 작업을 반복할 수 있습니다.

generate문은 테스트벤치에서 주로 쓰입니다.

for문은 c언어와 흡사합니다.

프로시저(Procedural Blocks): always, initial 블록 안에서 동작을 정의합니다. 각 블록은 특정한 이벤트에 대응하여 동작합니다.

함수(Function)와 태스크(Task): 모듈 내에서 작은 동작 블록을 함수나 태스크로 정의하여 코드의 모듈성을 높일 수 있습니다.

타이밍 제어(Force and Release): 디버깅을 위해 특정 시점에 시그널을 강제로 설정하거나 해제하는데 사용됩니다.

타이밍 제약(Timing Constraints): 시뮬레이션 동안 또는 합성 시에 회로의 시간적 동작을 제어하기 위해 사용됩니다.

클럭 동기화(Clock Edge Sensitivity): 클럭 동기화를 통해 특정 동작이 클럭 엣지에서만 동작하도록 할 수 있습니다.

이외에도 더 있지만 자주 사용하는 빈도 수 위주로 위에서부터 아래로 나열하였습니다.

'VERILOG' 카테고리의 다른 글

| Verilog - Combination Logic code(half adder,full adder,comparator,decoder)조합논리회로 (1) | 2024.02.14 |

|---|---|

| Verilog - DSP FIR Lowpass Filter(2MHz + 30MHz sin PHASE) (0) | 2024.02.13 |

| 조합논리회로 코드모음 (0) | 2024.02.02 |

| 순차논리회로 코드 모음 (0) | 2024.02.02 |

| Verilog HDL 문법(구조적(Structural),dataflow,동작적(Behaviroal)모델링,조합논리회로,순차논리회로) (0) | 2024.02.02 |